制造:

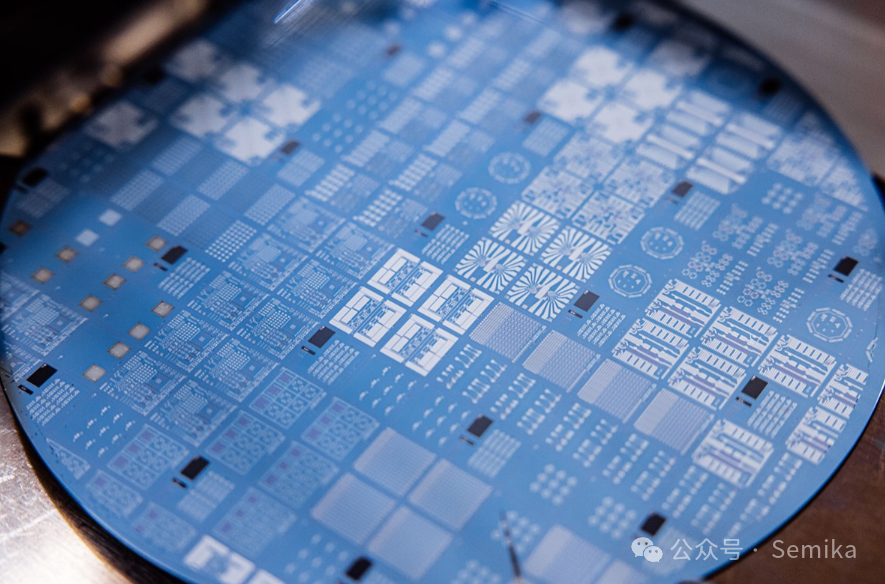

TAPEOUT(TO)流片:指提交最终GDSII文件给Foundry工厂做加工。

FULL MASK 全掩膜: 即制造流程中的全部掩膜都为某个设计服务。

MPW就是和别的厂家共享一张掩模版,而FULL MASK则是独享一张掩膜版。如果芯片风险比较高,则可以先做MPW,测试没有问题,再做FULL MASK。

SEAT:一个MPW的最小面积,就类似“班车”的座位,可以选择一个或者几个座位。一个SEAT就是3mm4mm。

Foundry晶圆厂: 专门从事芯片制造的厂家,例如台积电(TSMC),中芯国际(SMIC),联电(UMC)。对应的就是fabless,就是设计厂家,就是没有晶圆厂。

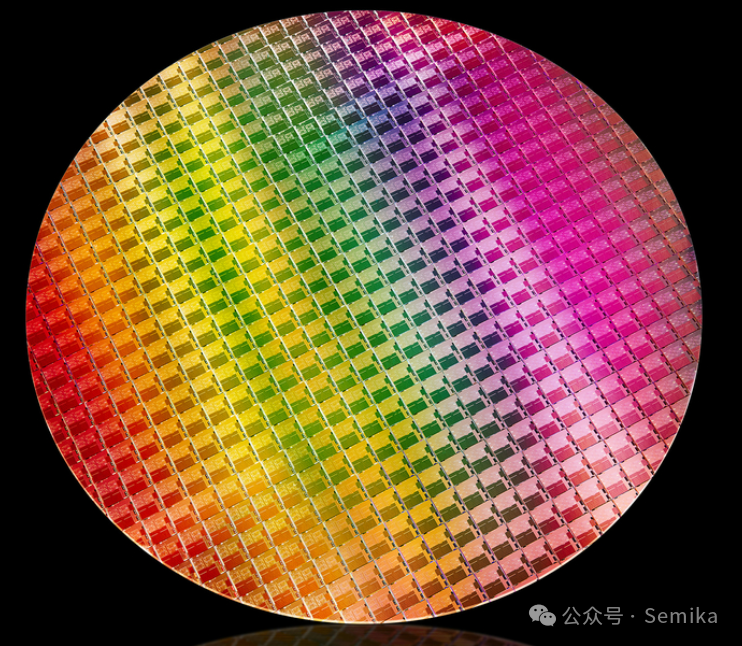

Wafer:晶圆。

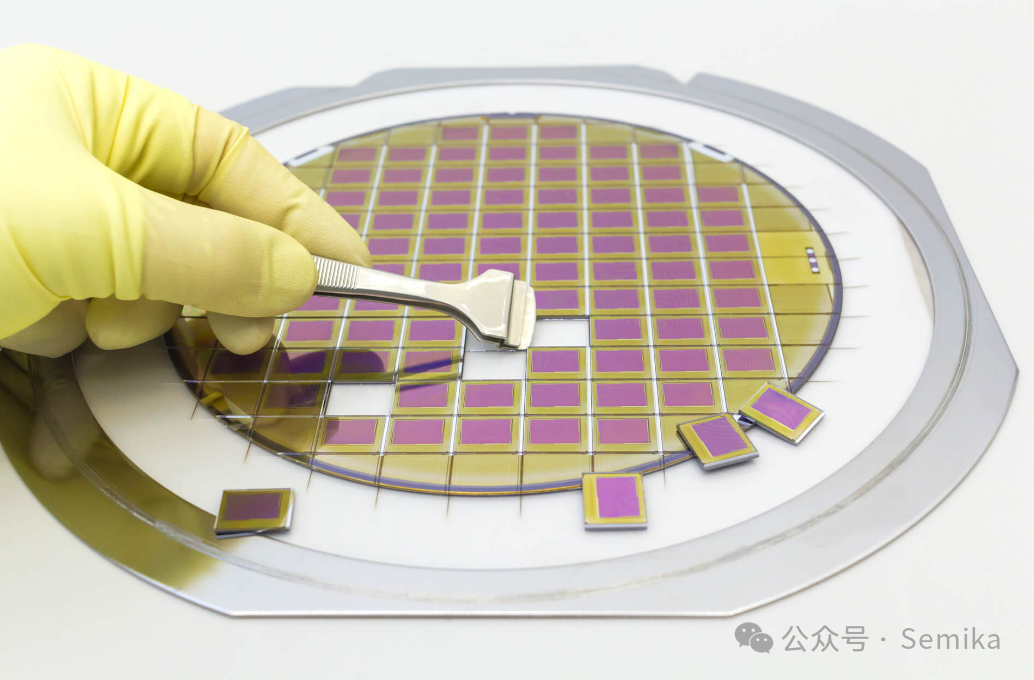

Die:晶圆切割后,单个芯片的晶圆,这个需要加上封装好的外壳才能能变成芯片。

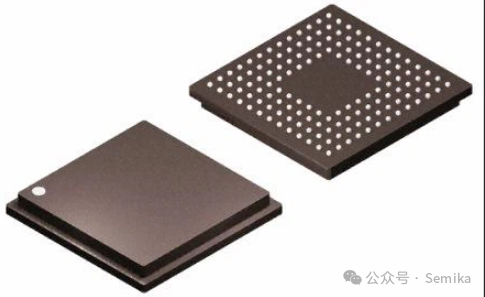

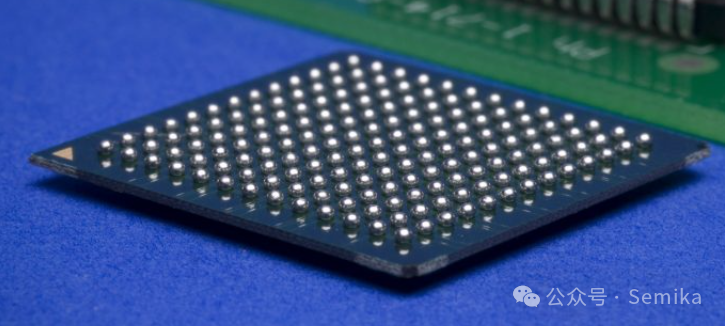

Chip:最后封装后的芯片。

Bump:bumping指凸点。在wafer表面长出凸点(金,锡铅,无铅等等)后,(多用于倒装工艺封装上,也就是flipchip)。

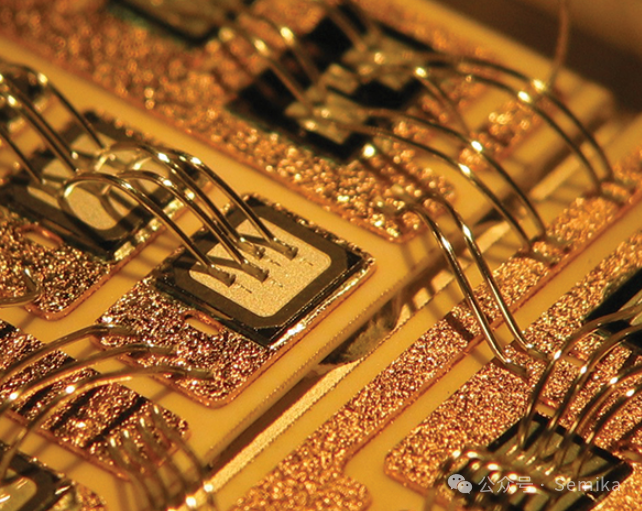

Wirebonding:打线也叫Wire Bonding(压焊,也称为绑定,键合,丝焊)是指使用金属丝(金线、铝线等),利用热压或超声能源,完成固态电路内部接线的连接,即芯片与电路或引线框架之间的连接。

Flipchip:Flip chip又称倒装片,是在I/Opad上沉积锡铅球,然后将芯片翻转加热利用熔融的锡铅球与陶瓷基板相结合。

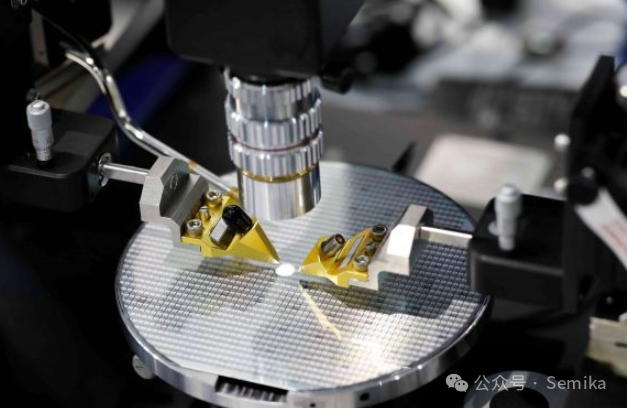

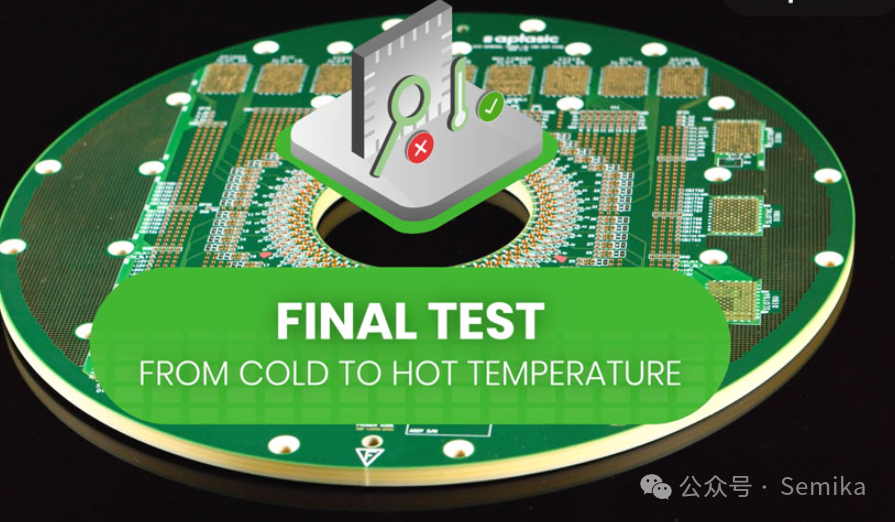

CP(Chip Probing):直接对晶圆进行测试,测试对象是针对整片wafer中的每一个Die,目的是确保整片wafer中的每一个Die都能基本满足器件的特征或者设计规格书,通常包括电压、电流、时序和功能的验证。可以用来检测fab厂制造的工艺水平。

CP针对晶圆,如果坏的Die就不用再去做封装了,省下封装的费用和基板的费用。

Yield 良率,芯片的良率这个和工艺比较相关,芯片有一定几率失效,芯片越大,失效机率也越大。

IP按收费方式分类可分为License, Loyalty。

license 授权许可:允许使用这个IP,IP的授权。

Loyalty 版税:在用户使用这个IP后,需要按照每个芯片收钱。

IP这个是构成芯片最核心的组成单元,例如USB,PCIE,CPU等等都是IP,整个芯片都是IP集成的,芯片能够做的比较复杂,核心就是IP的复用。例如那些做成几千万门,几亿门的,都是IP复用才能可以的。

SOC(System On Chip)片上系统,就是把CPU,总线,外设,等等放到一个芯片内部实现。例如手机处理器就是一个复杂的SOC芯片。

设计:

Register-Transfer Level(RTL)是用于描述同步数字电路的硬件描述语言。

Netlist 网表,RTL需要通过综合以后才能变成网表。

SDC(Synopsys Design Chip) :设计提供约束文件,综合工具需要这个约束文件才能将RTL转换成netlist。SDC主要描述内容包括:芯片工作频率,芯片IO时序,设计规则,特殊路径,不用check的路径等等。

Freeze指设计冻结,不能再改动的了,例如RTL freeze ,就是代码冻结了,netlist freeze 就是网表冻结了,不能再改了。

Verification芯片功能验证,主要指芯片验证方法论,验证RTL和reference model是不是一致。

Simulation仿真, 仿真通常是生成波形,一般来说,芯片的功能,verification ,芯片的功耗,可以simulation,比较直观反映真实的场景。

"添加小助手申请进群"

(icspec——规格书查询、免费发ic需求)