我们在文章《ACLR 和 ACPR》中,又复习了一边ACLR 的定义,但是在实际设计中,仅仅掌握这些定义是远远不够的。在射频系统设计中,尤其是PA设计中,遇到ACLR比较差的情况,到底该怎么办呢?

千人千面,对于ACLR这个问题,实际设计遇到的问题往往千奇百怪,尤其是对射频这个非常玄学的科目来说,每个人遇到的情况可能还不太一样,解决方案也不尽相同。

今天射频学堂整理了网络上一些同学的问题和解决方案,希望大家能够有所启发。

问题一请教关于ACLR的一个问题

ACLR是对相信信道产生干扰的一个衡量指标,但是具体可造成的原因是什么原理方面的?

精彩回复:

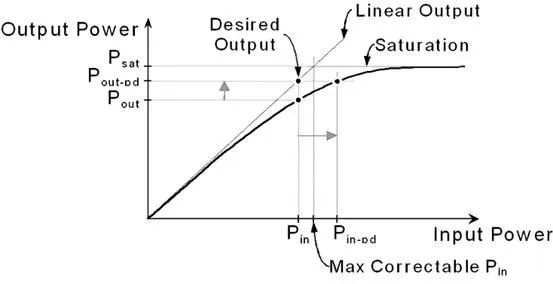

当你输出功率太大 会使PA操作在饱和区 产生非线性效应

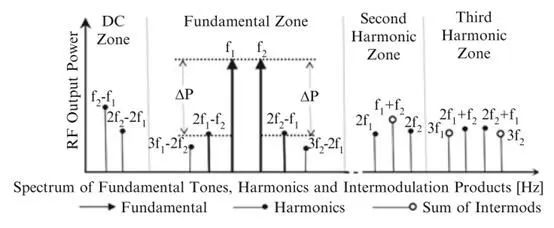

而非线性效应,会衍生许多噪声,例如 DC Offset,谐波,以及IMD (InterModulation),如下图 :

而三阶的IMD,即IMD3,其带宽会是讯号的三倍 因此会使两旁频谱上涨

而IMD3 又牵扯到IIP3 IIP3越大 其产生的IMD3就越小,所以简单讲 ACLR就是TX电路IMD3的产物,测ACLR 等于是在测你TX电路端的IIP3

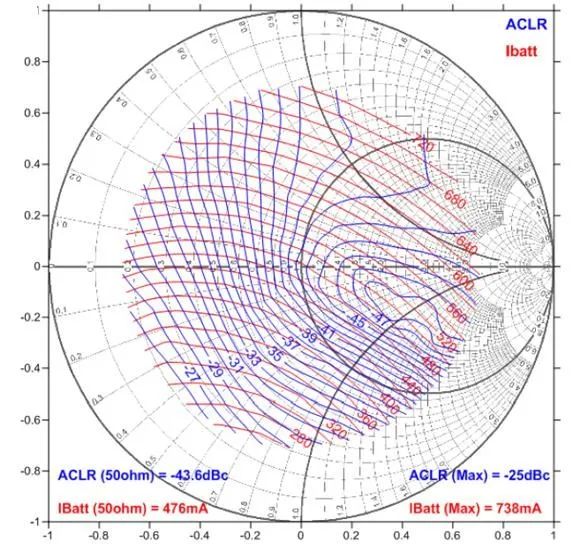

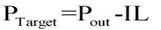

由上式可知 如果输入功率小 使PA操作在线性区或是这颗PA的IIP3够大 那么ACLR就可以压低。另外 厂商多半会有PA的Load pull图

由上图可知 ACLR跟耗电流是Trade-off,这是因为PA的线性度与效率 是反比的,你ACLR要低 那就是IIP3要高 线性度要好 因此效率就低 耗电流就大,反之 你要耗电流小 那就是牺牲线性度 ACLR就会差,所以一般而言 调PA的Load-pull时 多半就是调到最常用的50奥姆,以兼顾ACLR跟耗电流。

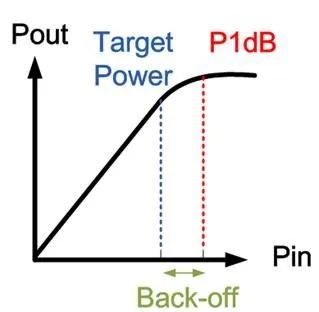

WCDMA的TX是BPSK调变 非恒包络,因此其PA须靠Back-off 来维持线性度,当然 Back-off越多 线性度越好(但耗电流也越大)

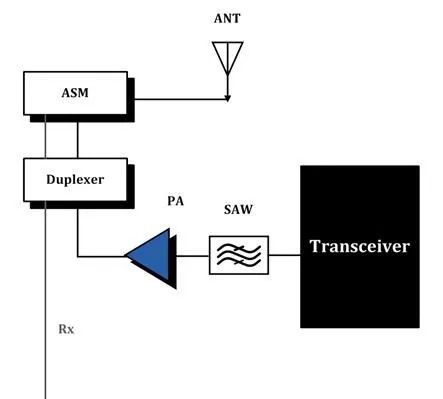

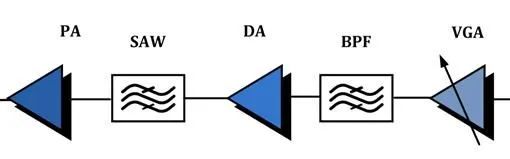

而WCDMA的方块图如下

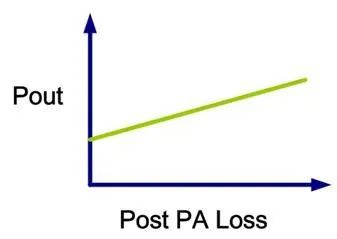

PA输出端的Loss 例如ASM, Duplexer, Matching, 走线的Insertion Loss,统称为Post Loss,如果你要达成Target Power(例如23.5 dBm),一旦Post Loss越大 意味着你PA的输出功率就越大 如下式跟下图 :

如果PA输出功率打越大 那就是Back-off越少 越接近饱和点,当然其线性度也越差 其ACLR会跟着劣化。

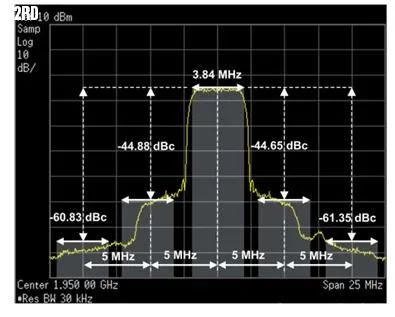

如下图

由上图可知 PA的input 同时也是DA(Driver Amplifier)的Load-pull,如果PA input的阻抗 离50奥姆太远,亦即此时DA的线性度不够好 ACLR就差,加上PA是最大的非线性贡献者,如果PA input的ACLR已经很差 那么PA out的ACLR 只会更差,一般而言 一线品牌大厂,其PA输出端 正负5MHz的ACLR,都要求至少-40 dBc。

亦即表示PA input的ACLR 至少要小于-50 dBc(由于DA的输出功率 远小于PA输出功率 因此ACLR也会来得较低再次证明ACLR与输出功率有关)。

LO Leakage跟DA产生的2倍谐波,有可能会在PA内部,产生IMD3

进而使ACLR劣化。

所以若在PA前端,先用SAW Filter把2倍谐波砍掉,可降低其IMD3

进一步改善ACLR。

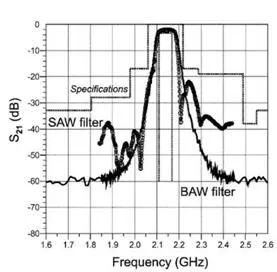

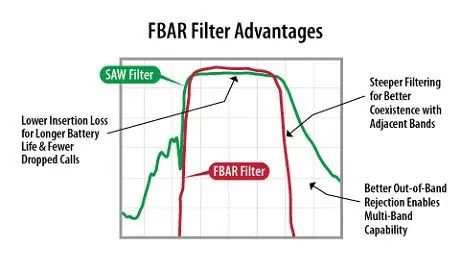

而若滤波器的陡峭度越好,则越能抑制带外噪声,因此理论上,使用BAW的ACLR,会比使用SAW来得好。

而FBAR的带外噪声抑制能力 又会比BAW来得好。

当然,有些平台,在PA前端,是没加SAW Filter的。而拿掉SAW Filter之后,其ACLR也不会比较差。

这是为什么呢?

其实由以上分析可以知道,PA前端的SAW Filter,之所以能改善ACLR,主要原因是抑制Transceiver所产生的Outband Noise(包含谐波)。

换言之,倘若Transceiver的线性度够好,所产生的Outband Noise很小,其实PA前端是可以不用加SAW Filter的,

但要注意 虽然PA前端的SAW Filter可抑制带外噪声,改善ACLR,但若其PA输入端SAW Filter的Insertion Loss过大,意味着DA需打出更大的输出功率 以符合PA的输入范围,(若低于下限 则无法驱动PA) 如下式 :

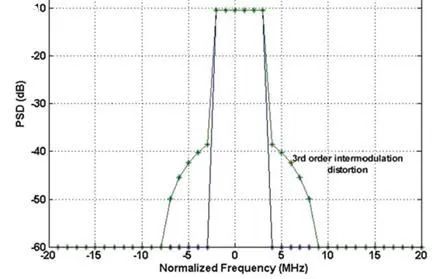

而不管是PA, 还是DA, 若输出功率越大,则ACLR越差, 如下图 :

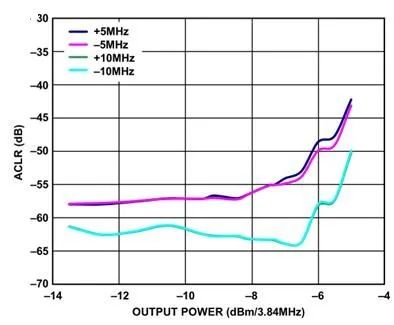

若DA输出功率大 使得PA输入端的ACLR差,那么PA输出的ACLR 肯定只会更差,当然 若用FBAR 既可抑制带外噪声 Insertion Loss又小 是个风险低的方案,但成本不低。由下图可知 Vcc越小 其ACLR越差

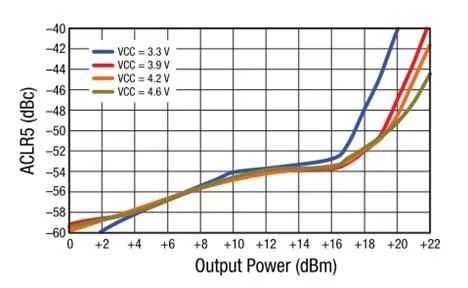

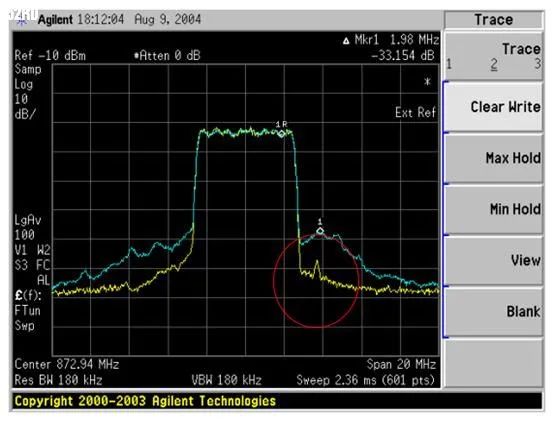

这是因为 放大器在闸极与汲极之间,会存在一个既有的寄生电容,又称为米勒电容,即Cgd,如下图 :

而当电压极低时,其Cgd会变大。

上式是Cgd的容抗,当Cgd变大时,则容抗会变小,因此部分输入讯号,会直接透过Cgd,由闸极穿透到汲极,即上图中的Feedthrough现象,导致输出讯号有严重的失真。简单讲 低压会让PA线性度变差

因此若Vcc走线太长或太细 会有IR Drop 使得真正灌入PA的Vcc变小

那么ACLR就会差

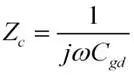

当然 除了PA电源 收发器的电源也很重要,否则若DA的电源因IR Drop而变小 使得PA输入端的ACLR变差,那PA输出端的ACLR 只会更差。在校正时 常会利用所谓的预失真 来提升线性度

而由下图可知 做完预失真后 其ACLR明显改善许多(因为提升了PA的线性度)

因此当ACLR差时 不仿先重新校正一下

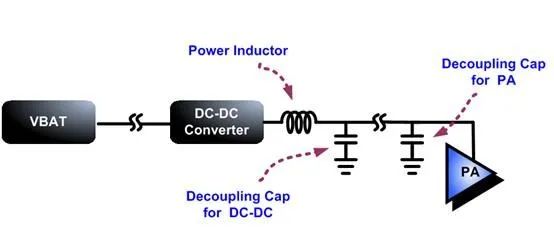

8. 一般而言 PA电源 是来自DC-DC Converter,其功率电感与Decoupling电容关系如下 :

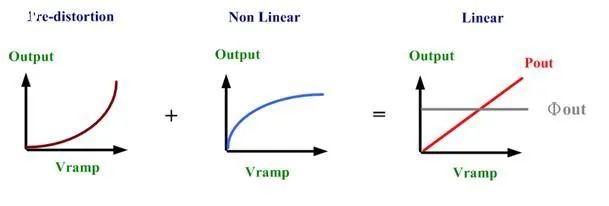

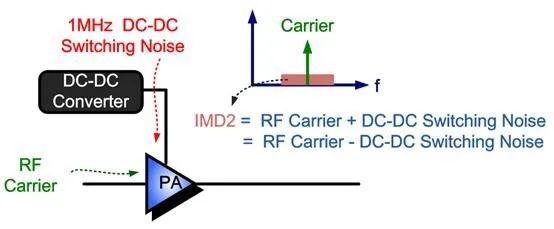

由于DC-DC Converter的Switching Noise 会与RF主频产生IMD2

座落在主频两侧

虽然IMD2的频率点 只会落在主频左右两旁1MHz之处,理论上不会影响正负5MHz的ACLR,但因为一般而言 DC-DC Converter的Switching Noise,其带宽都很宽 大概10MHz,因此上述IMD2的带宽 分别为5MHz与15MHz,(WCDMA主频频宽为5 MHz),换言之 上述的IMD2 是很宽带的Noise,故会影响左右两旁正负5MHz的ACLR

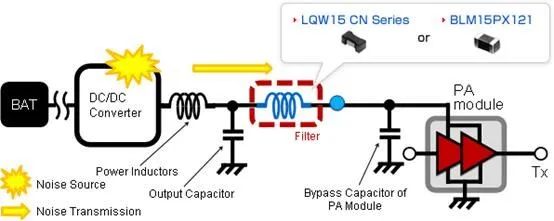

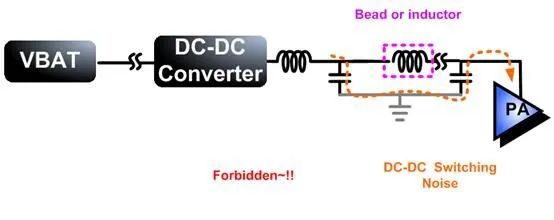

因此 如果能有效抑制DC-DC Converter的Switching Noise,便可抑制其IMD2, 进一步改善ACLR,故可利用磁珠或电感 来抑制DC-DC Converter的Switching Noise,如下图 :

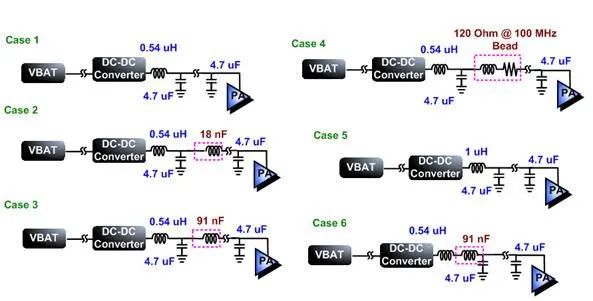

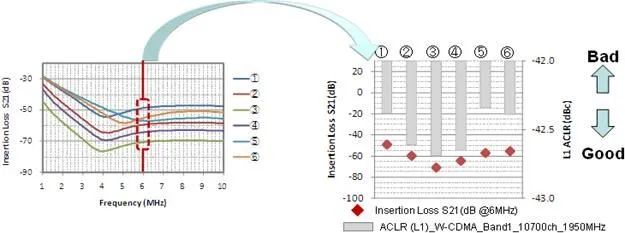

我们作以下6个实验

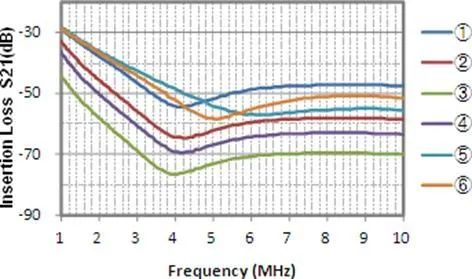

就假设DC-DC Switching Noise为1 MHz,我们可以看到 在Case2, Case3, Case4,其1 MHz的Insertion Loss都变大,这表示在DC-DC,PA的稳压电容之间 插入电感或磁珠,对于Switching Noise 确实有抑制作用,而由下图可知 其WCDMA的ACLR 也跟着改善,由于Case 3的Insertion Loss最大 因此Case 3的ACLR也确实改善最大

9. 承第8点 DC-DC Converter的稳压电容 与PA的稳压电容,绝不可共地,因为该共地 对DC-DC Switching Noise而言,是低阻抗路径 若共地,则DC-DC Switching Noise 会避开磁珠或电感,直接灌入PA 产生IMD2 导致ACLR劣化,换言之 共地会使第8点的磁珠或电感 完全无抑制作用

而功率电感, 磁珠或电感的内阻 也不宜过大 否则会产生IR Drop,使PA线性度下降 ACLR劣化

因此总结一下 ACLR劣化时 可以注意的8个方向

2. PA Load-pull

3. PA Post Loss

4. PA的输入阻抗

5. PA输入端的SAW Filter

6. Vcc的IR Drop

7. 校正

8. DC-DC converter Switching Noise

问题 二急 求降ACLR!

Avago的pa band2 高端信道aclar临界,大侠们有没有什么好的方法能把aclr降下去,不胜感激!

精彩回答

楼上正解,调试匹配可解:

矢网上看一下PA的负载阻抗是否收敛,且在ACLR与效率的折中处。如果不够聚拢,需要调双工器公共端匹配,先收敛,再调PA输出匹配。

问题 三请教ACLR、ACPR和Tx conducted spurious emission的异同?

请问ACLR、ACPR和传导杂散三者的异同点?

在射频指标测试验证时?

ACLR(WCDMA考量的?)

ACPR(CDMA考量的?)

TX Conducted Spurious Emission是都要考量的指标?

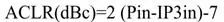

貌似ACLR和IMD3之间还有个换算关系

精彩回答

ACPR/ACLR: 指邻道功率泄露比

Spurious Emission:所有杂散的Mask

CDMA2000:ACLR(dBc)= 2(Pin-IIP3)-18.3

WCDMA:ACLR(dBc)= 2(Pin-IIP3)-9.2

TD-SCDMA:ACLR(dBc)= 2(Pin-IIP3)-8.3

精彩回答

并不是只跟匹配有关系。在匹配无大问题的情况下,我一般从以下几个方面来解决。毕竟ACLR是反映通路的线性度。所以主要提高线性度方面考虑。

1、如果用的APT供电方式。可以将相应电压提高,优化线性度

2、降低发射功率,通过修改NV或者修改校准参数都可以降功率,优化线性度,当然前提是你的功率不错。

3、可以从校准方面着手,例如修改一下参考信道,或者修改一下char的参数。

4、另外可以注意一下静态工作电流是不是合适,这个可以跟PA厂家沟通。

当然从load pull上偏向ACLR优化一下更直接。

主要还是看在loadpull上的位置和通路损耗,不过现在高通平台上用了ET技术,各种校准参数影响同样很大,具体情况具体分析

PA的供电也会影响ACLR,APT技术是为了省电,所以会使用一个相对低的电压,但是这个电压如果太低会造成PA的ACLR超标

影响ACLR的因素很多。输入功率,输入匹配,输出匹配,电源等。曾经遇到过,VCC的旁路电容对ACLR影响很大。

VCC旁路电容一般PF一个UF一个NF一个,主要是调制信号非恒包络引起的DC节点阻抗变化,导致电源电压压降产生低频信号与射频信号在输出处二次混频落到主频的临道。一般成熟的PA不会因为电源问题导致ACLR太差,只要旁路电容靠近PA pin就可以~

如果用了ET,那就要用到两方面的高通技术,一个是ET本身,还有一个就是DPD,其中DPD能提升线性度,而ET本身是为了省电。

ET需要做各种char校准来让ET工作在最好的状态,其中对ET delay,是为了让各信道电压包络和信号相位差最小,PinPout是补偿各信道不平导致的压缩程度的偏差。

ACLR是相邻信道功率抑制比,考察的是本信道的信号由于非线性引起的再生频谱,落在在相邻信道里的功率。这个考察的是对相邻信道的干扰。

EVM是误差矢量幅度,表征的是发射信号的调制质量,包含信号的幅度和相位的失真,不只是PA的恶化,在PA的输出,EVM是累积了发射机的所有的元件带来的恶化。当然PA是最后一级,恶化的贡献最大,EVM差,就是信号质量差,接收机解调的输出的误码率自然就差。

注释:上面问答整理自网络,仅供学习参考,如有侵权,请联系删除。

您在设计中还遇到过什么神奇的case?欢迎留言讨论。

||扫描上面二维码,即可加入射频学堂VIP,获取1000+学习资料 ||广告,商务合作,会议推广等,请 + VX:RF_Centered 版权声明:射频学堂原创或者转载的内容,其版权皆归原作者所有,其观点仅代表作者个人,射频学堂仅用于知识分享。如需转载或者引用,请与原作者联系。射频学堂转述网络文章,皆著名来源和作者,不可溯源文章除外,如有异议,请与我们联系。