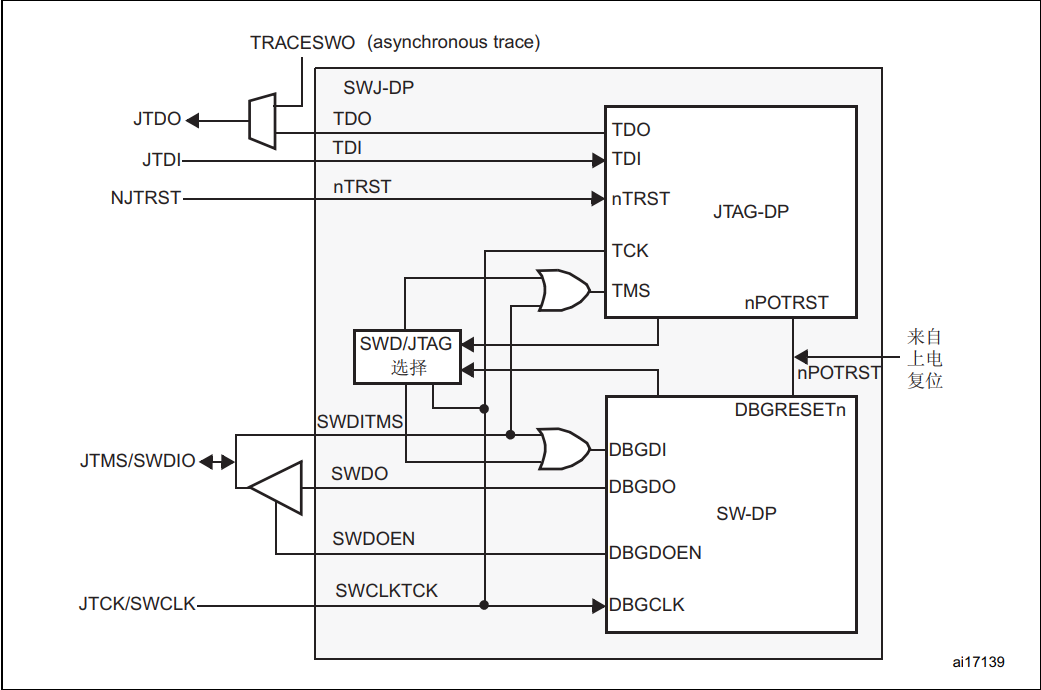

TDI:Test Data In。串行输入引脚 TDO:Test Data Out,串行输出引脚 TCK:Test Clock,时钟引脚 TMS:Test Mode Select,模式选择(控制信号)引脚 TRST:Test Reset,复位引脚

SWDIO:Serial Wire Data Input Output,串行数据输入输出引脚 SWCLK:Serial Wire Clock,串行线时钟引脚

其中SWD只需要两根线(SWCLK和 SWDIO),在PCB布局有限、引脚资源紧张的情况下,SWD算是一种不错的选择。

SWD简介

调试接口

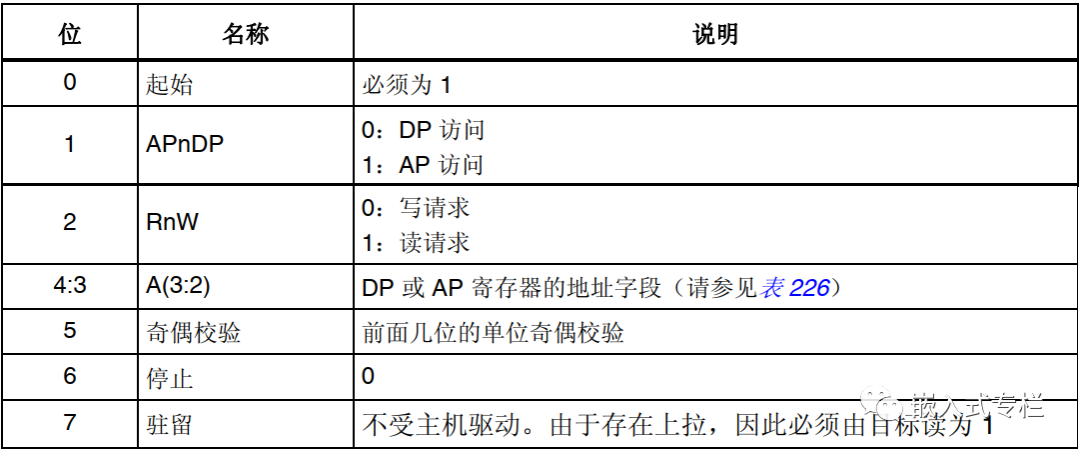

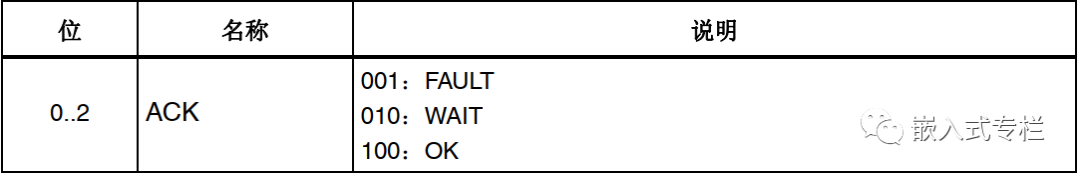

SW 协议序列

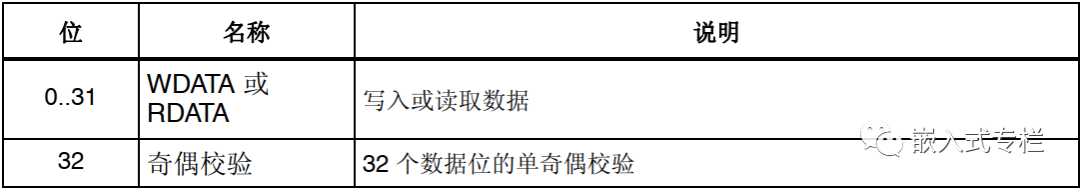

主机发送的数据包请求( 8 位) 目标发送的确认响应( 3 位) 主机或目标发送的数据传输阶段( 33 位)

SW-DP 状态

在上电复位后、 DP 从 JTAG 切换到 SWD 后或者线路处于高电平超过 50 个周期后,SW-DP 状态机处于复位状态。 如果在复位状态后线路处于低电平至少两个周期, SW-DP 状态机处于空闲状态。 复位状态后,该状态机必须首先进入空闲状态,然后对 DP-SW ID CODE 寄存器执行读访问。否则,目标将在另一个事务上发出 FAULT 确认响应。

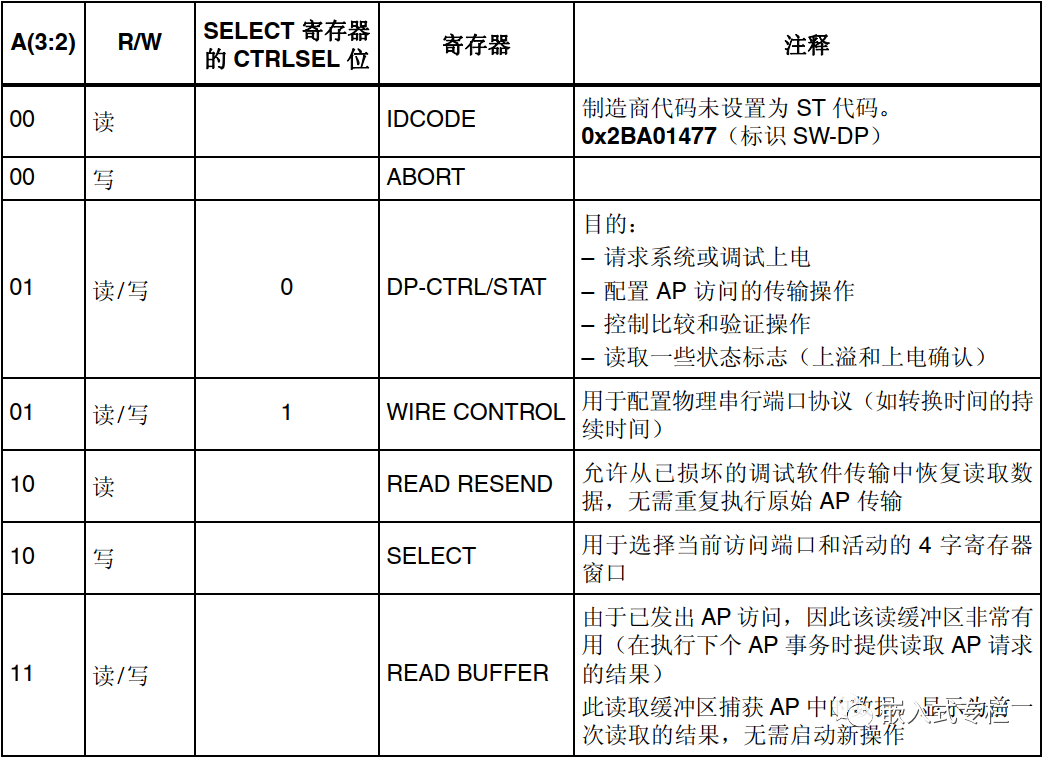

SW-DP 寄存器