在2022年IEEE超大型集成电路技术与电路研讨会上,英特尔(Intel)首度揭露有关Intel 4制程(原称Intel 7纳米;下称I4)的技术细节,以及Meteor Lake运算芯片块的照片。位于美国俄勒冈州Hillsboro的晶圆厂,将首先导入I4制程,下一个大概会是爱尔兰厂。

综合Tom’s Hardware与Forbes报导,当初英特尔发展10纳米制程的时候,希望能达到2.7倍于14纳米的晶体管密度,却因目标过于远大,许多新技术无法配合之下,出现10纳米制程无法及时达成量产目标的事故,并推迟EUV微影设备的使用,引发后续在制程技术上落后台积电、在CPU效能竞逐上不敌超微(AMD)等一连串问题。

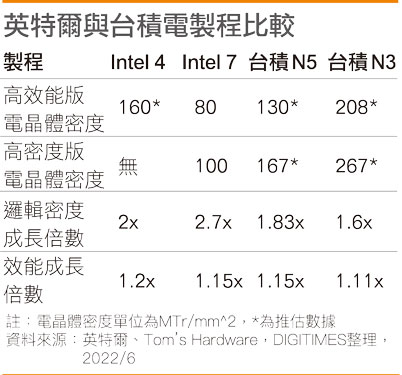

之后英特尔在推进至I4以下节点时,显然采取渐进式的步调导入新技术,避免重蹈覆辙:相较上一代的I7制程(10纳米强化Super Fin),I4能为芯片带来2倍的晶体管密度,符合摩尔定律的定义,并在功耗一致的前提下,改善20%效能;若以同等效能为前提,则可减少40%功耗。

与台积电相似,英特尔每个制程节点通常会有2种版本,一为高密度版,牺牲效能也要尽可能增加晶体管数量;另一则为牺牲晶体管密度换取效能的高效能版。然而I4没有高密度版,下一代I3才会恢复推出2种版本。已知I7高效能版的晶体管密度为80MTr/mm2,因此推测I4为160 MTr/mm2,落在台积电可比较的N5与N3制程之间。

相较于I7每个FinFET晶体管有4片鳍(fin),I4只有3片,能够缩小芯片所需面积。一般来说,鳍尺寸愈小、数量越少,会增加晶体管通道电阻,拉低FinFET效能,但英特尔表示,透过覆盖着钴金属的强化版铜线,降低在芯片中较低层的金属信号层的走线阻抗,降低I4所需鳍数。I4的金属绝缘层金属(MIM)电容密度也翻倍,应能大幅改善芯片持续性的时脉速度。

作为过渡性质的制程,I4也是英特尔第一个导入并广泛使用EUV微影技术的节点,有助于提升良率。英特尔前后端制程都会使用EUV,因此I4虽比起I7更为先进,但制程步骤与光罩数量反而还分别少5%与20%。以I4来说,若使用传统DUV浸润式微影技术,1层需要5个光罩来曝光,但EUV只要1个;若无EUV的帮助,I4制程步骤会多于I7。I4将于2022年下半准备投产。

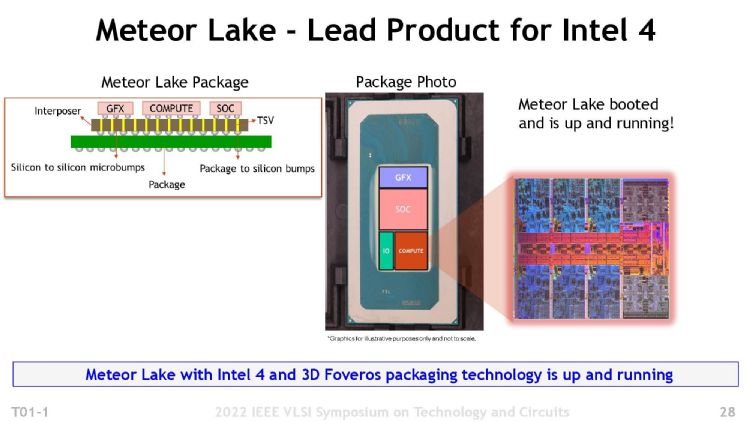

即将于2023年上市的第14代Core处理器Meteor Lake,为英特尔首款导入I4制程的客户端PC处理器,采用小芯片设计与3D Foveros封装技术。Meteor Lake透过矽通孔(TSV)垂直互连技术,将运算、I/O、SoC、绘图共4个芯片块,与置于其下的中介板(interposer)相连。至于中介板为主动或被动式、或是否含有快取或其他控制电路则未知。

已知Meteor Lake运算芯片块将采I4制程,但其他芯片块未知。在先前的技术蓝图中,Meteor Lake项下,除了I4以外,还有标注外部N3制程,外界推测应指台积电,可能用于绘图等芯片块。Meteor Lake采x86混合架构,运算块含6颗Redwood Cove效能核心及8颗Crestmont节能核心。芯片中央还有L3快取与互连电路。

继续往下推进:相较I4,I3导入EUV的层数增加,芯片速度将提升18%,也是英特尔晶圆代工服务(IFS)除现有16纳米之外提供客户使用的第一个新制程。值得注意的是,Xeon处理器Granite Rapids推出时程从2023年推迟至2024年,原因就在于采用制程从I4升级成I3;由于I4可向前兼容I3,因此转换所需时间并不长。

之后进入埃时代(angstrom era),Intel 20A与18A将舍弃FinFET,导入RibbonFET技术,透过垂直堆叠多个晶体管通道,大幅提升晶体管密度。比起FinFET闸极只能接触通道4面中的3面,RibbonFET闸极是完全环绕通道,能更好的控制晶体管电流,因此可带来更高的效能。